基于FPGA的数字时钟的设计与实现

本次设计的是一款数字时钟,且其具有多功能,该时钟具有时、分、秒计数的显示功能,其计数方式是以24小时循环的计数制,其次还具备闹钟、自动报时等特色功能。本次设计是使用硬件描述语言Verilog

HDL来进行设计,作为系统逻辑描述语言,其表达了逻辑系统所完成的逻辑功能以及逻辑电路图、逻辑表达式,具有覆盖面积广、抽象能力强等特点,在实际应用中越来越广泛。在Quartus

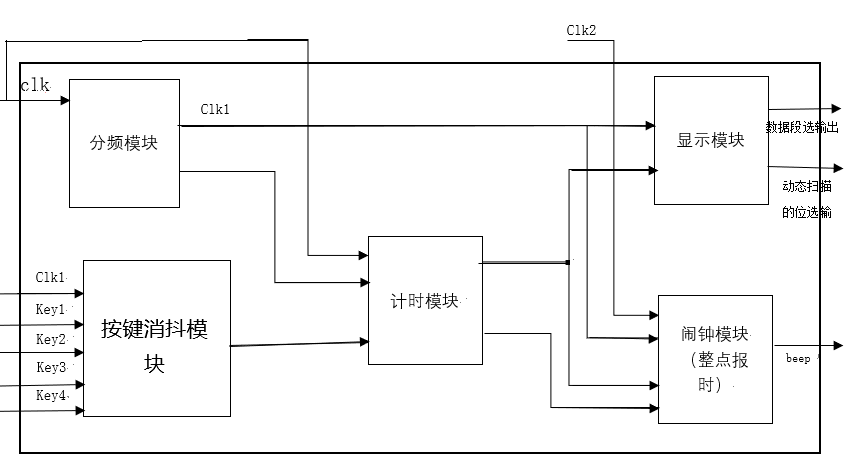

II工具软件的环境下,采用自顶而下的设计方法,再设计各个子模块,共同组成一个基于FPGA的数字时钟,再用Modelsim工具软件进行RTL仿真。而本次设计则是由分频模块、按键消抖模块、计时模块、显示模块以及闹钟模块组成。经过编译代码,以及仿真所设计的代码,并且在开发板上进行下载验证。本次设计可实现时、分、秒的显示,通过按键可进行校准,以及整点报时、闹钟等功能。

第1章 绪

论........................................................................................ 1

1.1 论文研究的意义与目的.......................................................................... 2

1.2 论文研究的内容与方法.......................................................................... 2

1.3预期目标................................................................................................. 3

1.4 课题研究现状......................................................................................... 3

1.4.1 从功能上来看......................................................................................................... 3

1.4.2 从研究趋势上来看................................................................................................. 3

第2章 关键技术介绍........................................................................... 5

2.1 总体功能................................................................................................. 5

2.1.1 整点报时功能......................................................................................................... 5

2.1.2 计时功能................................................................................................................. 5

2.1.3 时钟分频功能......................................................................................................... 6

2.1.4显示功能.................................................................................................................. 6

2.1.5闹钟功能.................................................................................................................. 7

2.1.6蜂鸣器功能.............................................................................................................. 7

2.2 FPGA开发原理......................................................................................... 7

第3章 基于FPGA的数字时钟的设计............................................. 9

3.1时钟分频模块.......................................................................................... 9

3.2计时模块................................................................................................. 9

3.3按键消抖模块....................................................................................... 10

3.4显示模块............................................................................................... 11

3.5闹钟设定模块....................................................................................... 12

第4章 基于FPGA的数字时钟的仿真结果.................................. 13

4.1 时钟分频的仿真................................................................................... 13

4.2 按键消抖功能的仿真............................................................................ 13

4.3 计时功能的仿真................................................................................... 13

4.4 显示功能的仿真................................................................................... 14

4.5 自动报时的仿真................................................................................... 14

4.6 板子里的实例验证............................................................................... 15

4.6.1 闹钟....................................................................................................................... 15

4.6.2 整点报时............................................................................................................... 16

4.6.3 调节时间............................................................................................................... 16

第5章 结 论............................................................................................ 18

整个多功能数字时钟的实现主要由于Verilog HDL语言编写的子模块连接而成,这些子模块程序包括时钟分频模块、计时模块、按键消抖模块、显示模块、闹钟模块等。系统模块框图如图

通过设计测试文件,验证时钟分频的仿真结果的正确性,时钟分频的仿真波形图如图所示。通过波形可以看出输入为50Mhz的时钟,通过分频得到1Khz时钟、500hz时钟、1hz时钟以及2hz时钟,从波形可以看出满足设计要求

- 微信

- 赶快加我聊天吧

- 开发交流群

- 海纳百川,大家来水