基于FPGA的实时操作系统的移植与应用

本次设计为基于FPGA的μC/OS-II实时操作系统的移植与应用,本设计采用EDA技术,以硬件描述语言Verilog

HDL为系统逻辑描述语言设计文件,在QUARTUS工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的实时操作系统的移植与应用。本设计将实现在FPGA上进行实时操作系统移植,通过获取µC/OS-II系统内核源码并修改、添加外设USB驱动、交叉编译生成映像文件、文件烧写到开发板上等步骤,其功能和应用包括数字时钟计时、蜂鸣器播放音乐的同时VGA进行视频文字显示。其中数字时钟具有时、分、秒计数显示功能,以24小时循环计数,可按键进行校准,整点报时。蜂鸣器可以播放梁祝音乐以及两只老虎音乐片段,可以通过开发板上的key1键控制播放和暂停,同时VGA可把通过字符转换工具将字符转换为8进制mif文件存放到单端口的 ROM IP 核中,再从ROM中把转换后的数据读取出来显示到 VGA 上。当数码管上显示FLASH的第一个字节时,通过按key1键,数字会加一,同时擦除了FLASH,并将新的数据写入,重新上电后,加载下载程序,数码管将显示最后一次按按键的数字。

第1章 绪

论............................................................................................................... 1

1.1 论文研究的目的与意义.............................................................................................. 1

1.2 国内外研究现状............................................................................................................ 1

1.3 论文预期成果................................................................................................................ 2

第2章 关键技术介绍............................................................................................... 3

2.1 μC/OS-II系统................................................................................................................. 3

2.2移植技术及方法............................................................................................................ 5

2.3 FPGA开发板及其核心芯片...................................................................................... 7

第3章 操作系统移植与实现............................................................................. 10

3.1 方案分析与设计.......................................................................................................... 10

3.2 实时操作系统移植..................................................................................................... 10

3.2.1移植文件的配置与修改....................................................................................... 11

3.3 实时操作系统移植的验证及应用......................................................................... 12

3.3.1 数码管时钟显示.................................................................................................. 13

3.3.2 带音乐播放的VGA文字显示.............................................................................. 14

3.3.3 SPI_FLASH控制器............................................................................................... 15

第4章 系统测试....................................................................................................... 20

4.1数码管时钟显示模块测试........................................................................................ 20

4.2带音乐播放的VGA文字显示模块测试............................................................. 20

4.3 SPI_FLASH控制器测试........................................................................................... 22

第5章 结 论............................................................................................................. 25

参考文献............................................................................................................................. 26

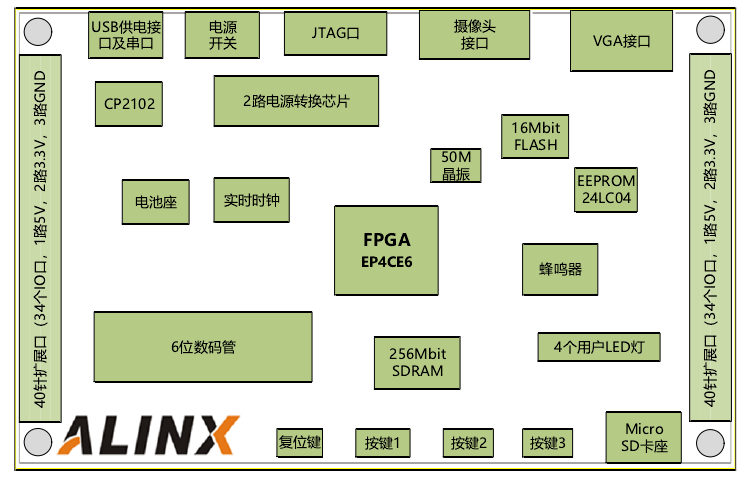

FPGA 型号:AX301_EP4CE6F17C8,核心芯片为M25P16(或者说EPCS16)实质是一个串行FLASH芯片,容量为16Mbit,对于存储FPGA中的程序来说,这个容量绰绰有余的。同时还可以存储软核NIOS-II的应用程序,因此,其作用在FPGA的设计中起到了至关重要的作用。此款开发板属于ALTERA 公司CYCLONE IV的产品。此型号为BGA封装,256个引脚,采用40nm工艺,芯片可编程规模为180K等效4输入LUT。整个开发板的配置实用,有两路黑金标准的40针2.54标准的扩展口,一共有34*2=68个IO,另外也引出了5V电源,3.3V电源,还有多路GND以及丰富的片上时钟资源等模块,广泛适用于通信、视频、工业控制等多个应用领域。AX301开发板组成单元如图

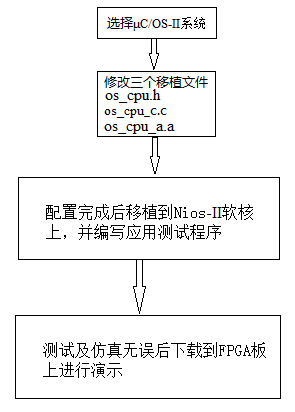

随着高端芯片价格的走低以及对嵌入式操作系统功能需求的不断增加,在当下主流的FPGA板上移植实时操作系统、配套相关服务并在此基础上建立紧密依赖于行业背景的专用系统日益成为嵌入式系统应用开发的主流趋势。对于项目的需求从实时操作系统的选择和开发板的选择出发,根据调研明确的选择了μC/OS-II实时操作系统和Altera旗下的AX301系列开发板。而在前面也说明了移植的相关步骤,即为通过获取µC/OS-II系统内核源码并修改、添加外设USB驱动、交叉编译生成映像文件、将文件烧写到开发板上等步骤。通过前面的需求分析和最终所要达到的目的,确定了一步步的操作流程,根据需求调查结果,确定系统移植操作流程图。其流程图如图

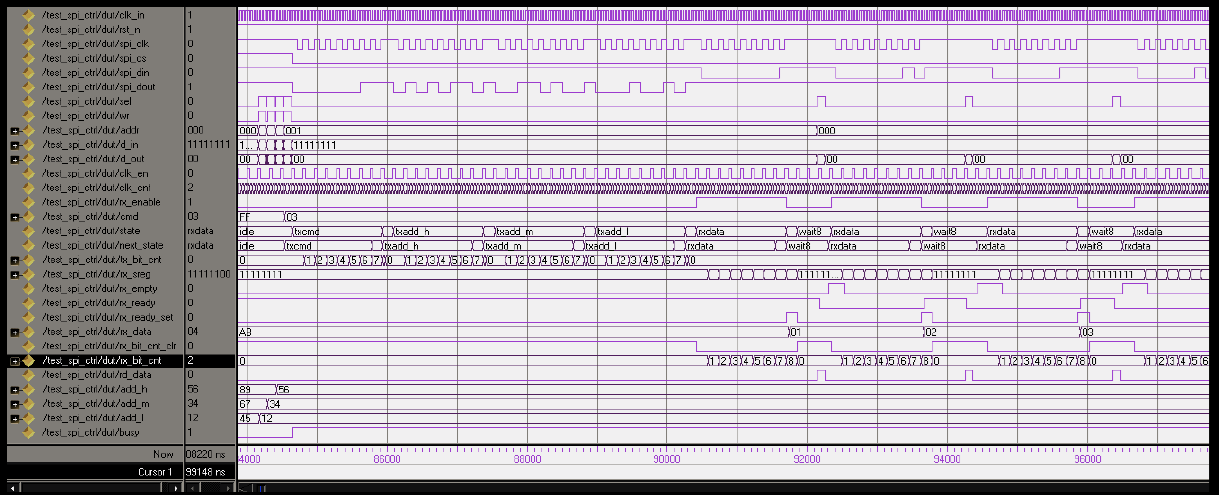

为了检验FLASH掉电不丢失的功能,实验设计了一个状态机,在上电一段时间后读取FLASH的第一个字节,并通过数码管将它显示出来,如果按键按下,将数字加1,再写回FLASH,这样下次上电会保持新写入的数据。SPI_MASTER状态机设计,主要完成一个字节SPI数据的读写,由于是全双工的,写一个字节的同时也读一个字节。首先空闲状态“IDLE”接收到写请求后进入“DCLK_IDLE”状态,这个状态为SPI时钟沿变化保持一定的时间,用来控制SPI时钟的周期,然后进入SPI时钟沿的变化状态,一个字节上升沿和下降沿一共16个数据沿。在最后一个数据沿进入“LAST_HALF_CYCLE”状态,为让最后一个沿也保持一定的时间,再进入应答状态,完成一次写请求。SPI_MASTER模块中模拟了一个SPI时钟,在状态机进入到“DCLK_EDGE”时进行翻转。FLASH读、写仿真图如下图

- 微信

- 赶快加我聊天吧

- 开发交流群

- 海纳百川,大家来水